Layout Diagrams for Combinational Circuits in VLSI

📑 10 slides

👁 38 views

📅 2/3/2026

Introduction to Combinational Circuits

Combinational circuits output depends only on current inputs, unlike sequential circuits.

2

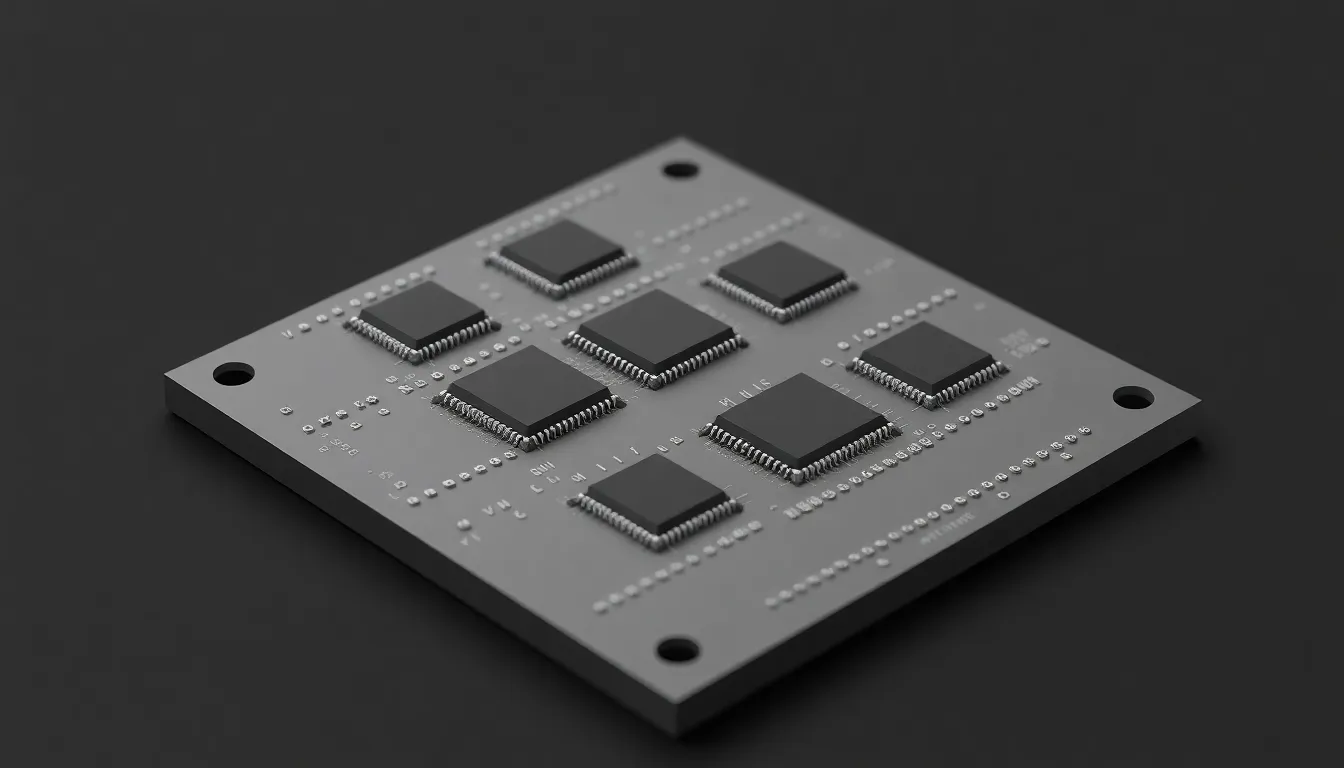

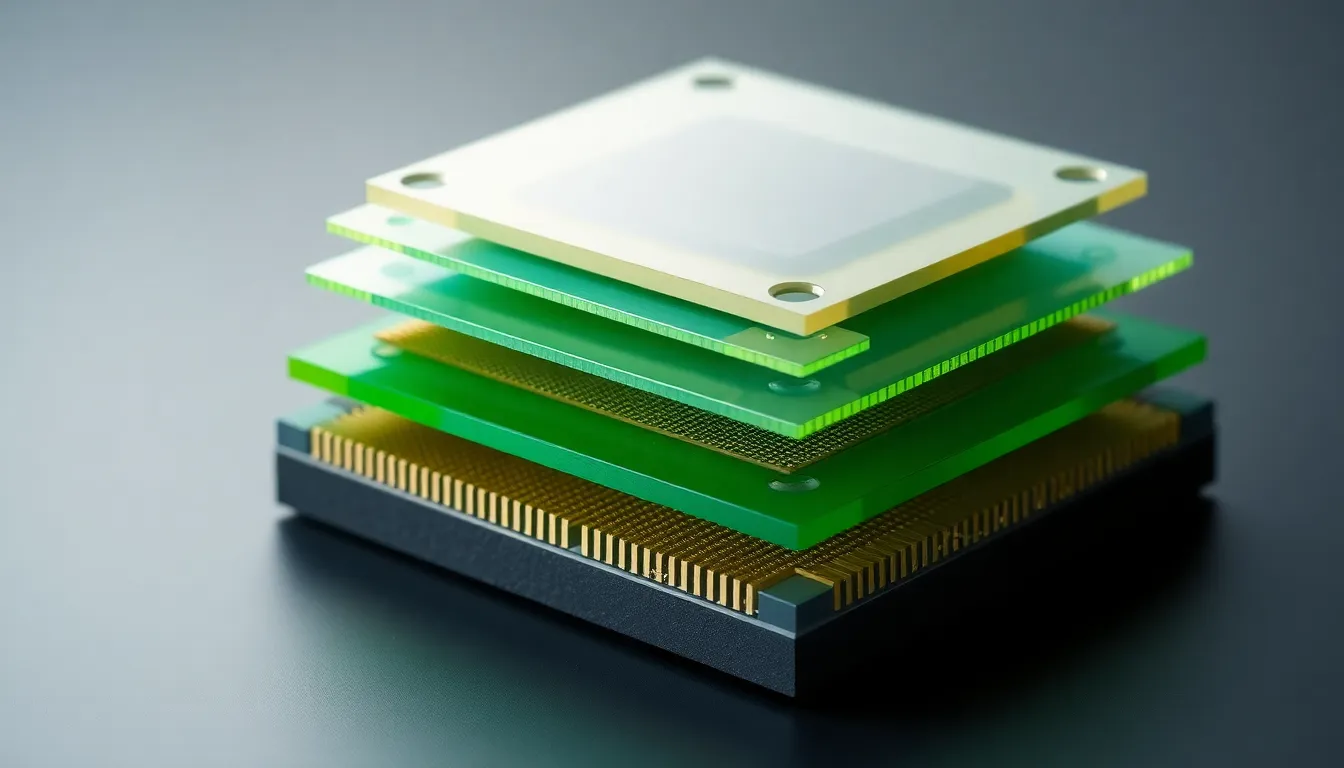

VLSI Design Basics

- VLSI (Very Large Scale Integration) integrates millions of transistors on a single chip.

- Design involves multiple layers: diffusion, polysilicon, and metal.

- Layout diagrams represent physical implementation of logic circuits.

3

Layout Diagram Components

- Transistors formed by intersections of diffusion and polysilicon layers.

- Metal layers used for interconnections between components.

- Vias connect different metal layers vertically.

4

Standard Cell Methodology

- Pre-designed logic cells (AND, OR, NOT) with fixed height but variable width.

- Enables automated placement and routing in digital designs.

- Power rails run horizontally at top and bottom of cells.

5

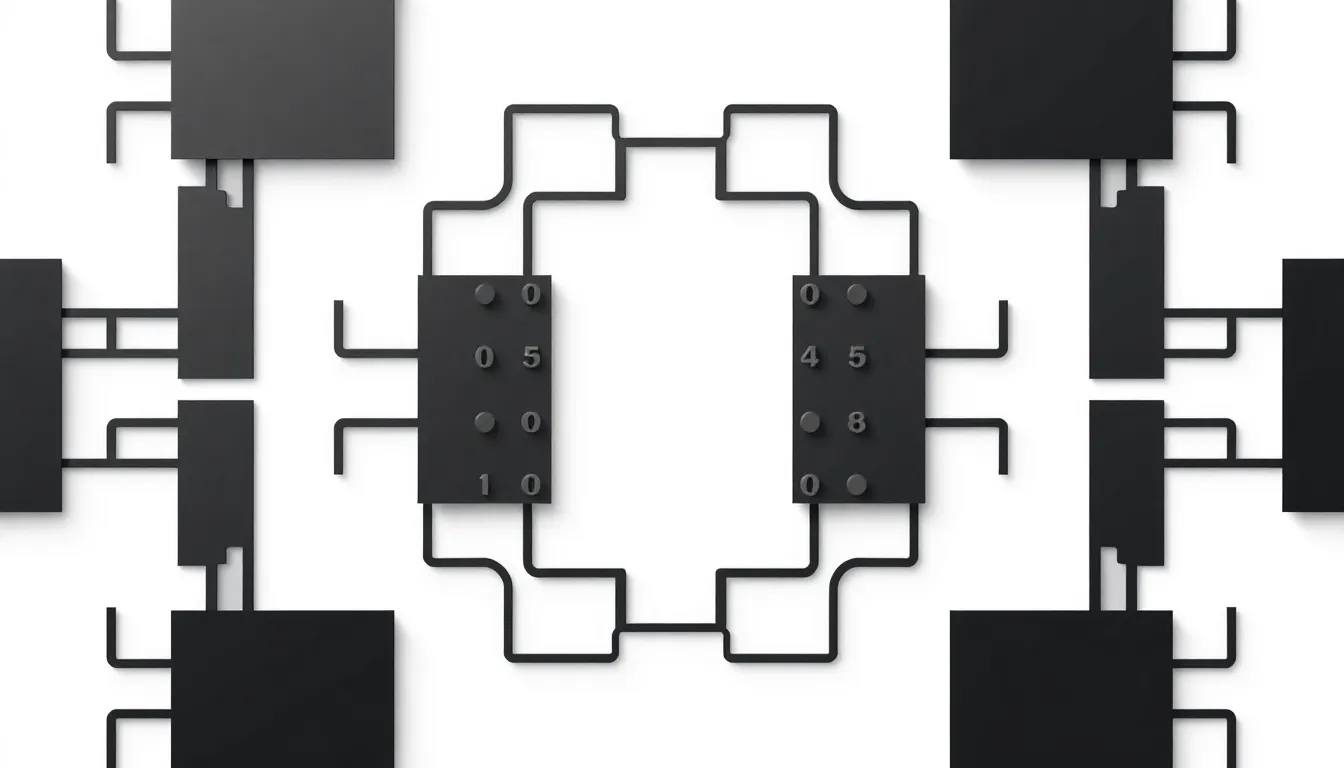

Stick Diagrams

- Simplified layout representation using color-coded lines for layers.

- Helps visualize routing before detailed layout design.

- Reduces design time by identifying routing conflicts early.

6

Design Rules and Constraints

- Minimum spacing between metal lines to prevent short circuits.

- Width requirements for different layers to ensure proper fabrication.

- Foundry-specific rules that must be strictly followed.

7

Common Combinational Circuits

- Full adder layout requires careful transistor sizing and placement.

- Multiplexer designs optimize for both speed and area efficiency.

- Decoder layouts expand exponentially with input bits.

8

Optimization Techniques

- Transistor sizing affects speed and power consumption.

- Routing optimization reduces wire length and parasitic capacitance.

- Cell folding techniques minimize area while maintaining functionality.

9

Verification Methods

- DRC (Design Rule Checking) ensures manufacturability.

- LVS (Layout vs Schematic) verifies functional equivalence.

- Parasitic extraction analyzes performance impact of interconnects.

10

Conclusion and Future Trends

- Layout design remains crucial as technology nodes shrink.

- Machine learning aids in automatic layout generation.

- 3D ICs introduce new challenges in combinational circuit layout.

1 / 10